Ppt The Cmos Inverter Powerpoint Presentation Free Downloadођ

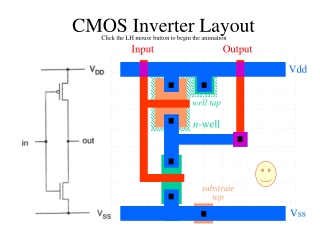

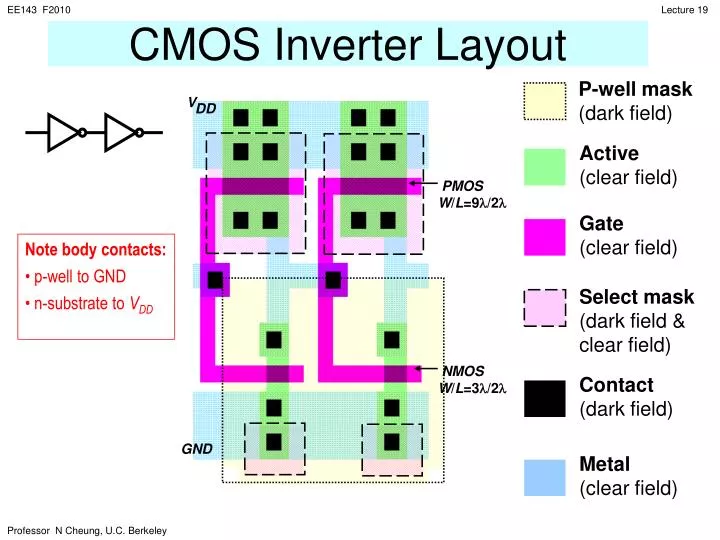

Ppt Cmos Inverter Layout Powerpoint Presentation Free Downloa Lecture 4: cmos inverter dynamics. inverter capacitances task: calculate cg and cdwith pmos fet is twice as wide as nmos fet expressed in the width of the nmos transistor. vdd w=2 rn,eff=2 kw.mm vin vout vin vout w=1 cg=3.6 ff mm cd=pinvcg vdd vss vss vss we notice that cg × rn,effis a constant. it will soon return!. The cmos inverter lecture 3 staticproperties = voltage transfer curves (vtc) and noisemargins. week 2: the cmos inverter • tuesday • static properties • voltage transfer curves (vtc) • noise margins • exercise (kjell, 1 hour) • thursday • dynamic properties • propagation delay • driving large capacitive loads w. optimal propagation delay • exercise potw (victor, 2 hours.

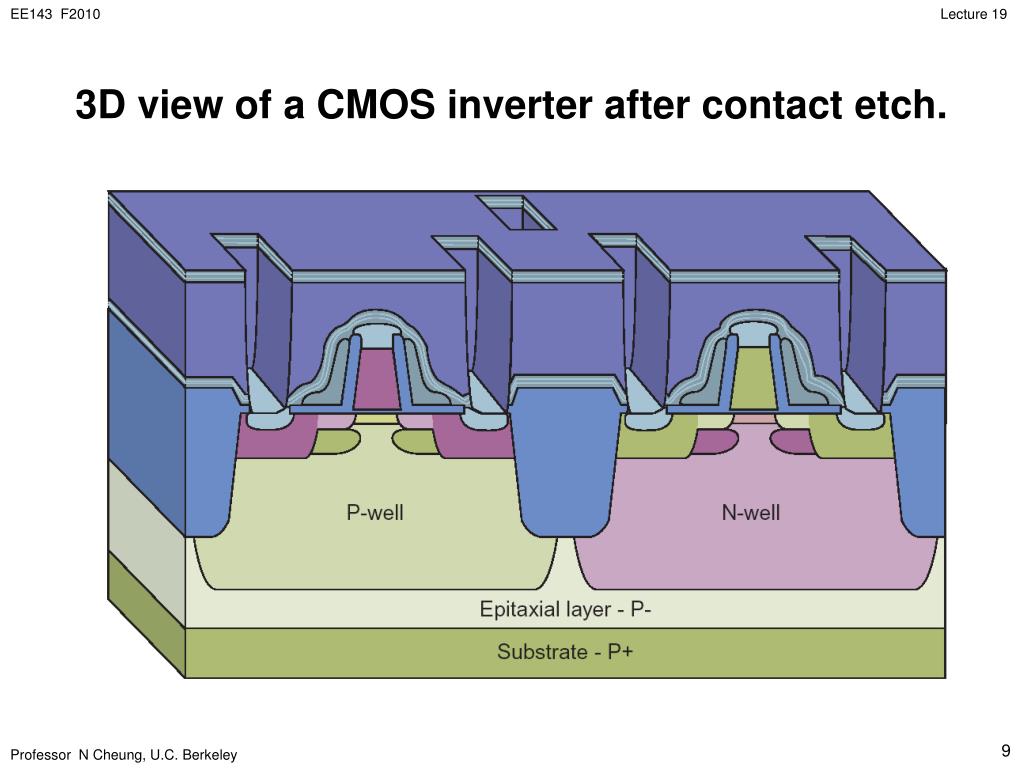

Ppt Cmos Inverter Layout Powerpoint Presentation Free Downloa Ee141. 1 digital integrated circuits2nd. devices. lecture 7. cmos inverter. ece 407 507 circuits2nd. devices. the cmos inverter: a first glance. v. in – a free powerpoint ppt presentation (displayed as an html5 slide show) on powershow id: 1632cf ymy4o. Cmos inverter. an image link below is provided (as is) to download presentation download policy: content on the website is provided to you as is for your information and personal use and may not be sold licensed shared on other websites without getting consent from its author. download presentation by click this link. The cmos inverter. regions of operation (balanced inverter) vin n mos p mos vout 0 cut off linear vd d vtnltvinltvdd 2 saturation linear vdd vdd 2 saturation saturation vdd 2 vdd vtpgtvingtvdd 2 linear saturation 0 vdd linear cut off 0. 4 the cmos inverter 5 the cmos inverter. propagation delay ; main origin load capacitance ; to reduce the. Title: chapter 5 cmos inverter. description: chapter 5 cmos inverter boonchuay supmonchai integrated design application research (idar) laboratory july 5, 2004; revised june 25, 2005 goals of this chapter – powerpoint ppt presentation. number of views: 3916. avg rating:3.0 5.0.

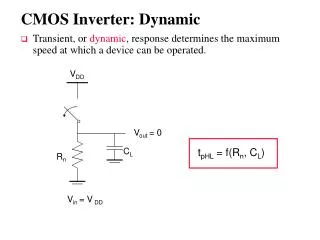

Ppt Cmos Inverter Layout Powerpoint Presentation Free Downloa The cmos inverter. regions of operation (balanced inverter) vin n mos p mos vout 0 cut off linear vd d vtnltvinltvdd 2 saturation linear vdd vdd 2 saturation saturation vdd 2 vdd vtpgtvingtvdd 2 linear saturation 0 vdd linear cut off 0. 4 the cmos inverter 5 the cmos inverter. propagation delay ; main origin load capacitance ; to reduce the. Title: chapter 5 cmos inverter. description: chapter 5 cmos inverter boonchuay supmonchai integrated design application research (idar) laboratory july 5, 2004; revised june 25, 2005 goals of this chapter – powerpoint ppt presentation. number of views: 3916. avg rating:3.0 5.0. Is the difference between the lowest acceptable ‘1’ and the highest possible ‘1’. nm. = v oh – v ih. t. phl is the propagation delay from the 50% point of the input to the output when the output goes from high to low. t. plh is the propagation delay from the 50% point of the input to the output when the output goes from low to high. Consider a simple inverter •when vin = 0 vout = vdd •when vin = vdd vout = 0 in between, vout depends on current through transistors as determined by transistor width and length by kcl, steady state condition is: •idsn = |idsp| find transfer function by solving equations, but better insight using graphical method.

Ppt Cmos Inverter Layout Powerpoint Presentation Free Downloa Is the difference between the lowest acceptable ‘1’ and the highest possible ‘1’. nm. = v oh – v ih. t. phl is the propagation delay from the 50% point of the input to the output when the output goes from high to low. t. plh is the propagation delay from the 50% point of the input to the output when the output goes from low to high. Consider a simple inverter •when vin = 0 vout = vdd •when vin = vdd vout = 0 in between, vout depends on current through transistors as determined by transistor width and length by kcl, steady state condition is: •idsn = |idsp| find transfer function by solving equations, but better insight using graphical method.

Comments are closed.