Pass Transistor Logic Static Cmos Circuit Design Vlsi Lec 93

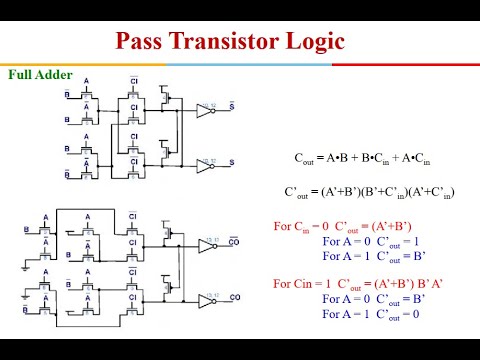

Pass Transistor Logic Static Cmos Circuit Design Vlsi Lec 93 Vlsi static cmos circuit designpass transistor logic in static cmos circuit designusing nand & or gates lec 92 : youtu.be fnggm qykomlec 94 : https:. High noise margins. z v and v. oh ol are at v and dd gnd, respectively. low output impedance, high input impedance. no static power consumption. z never a direct path between. v. dd and gnd in steady state. delay a function of load capacitance and transistor on resistance comparable rise and fall times (under the appropriate relative transistor.

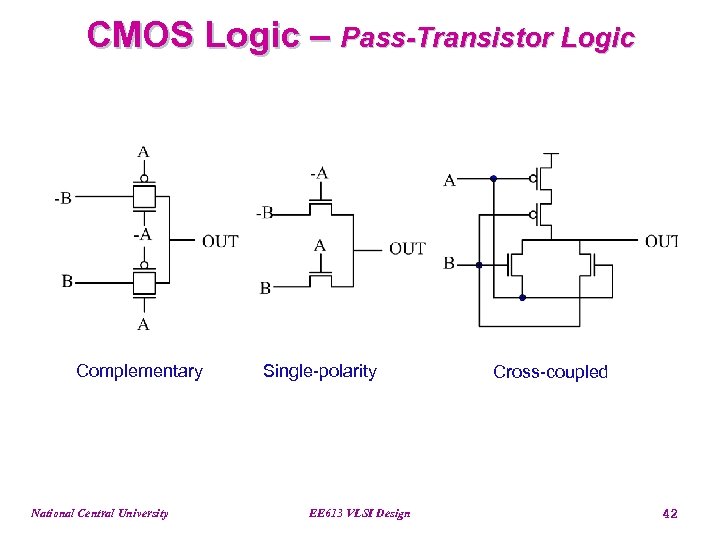

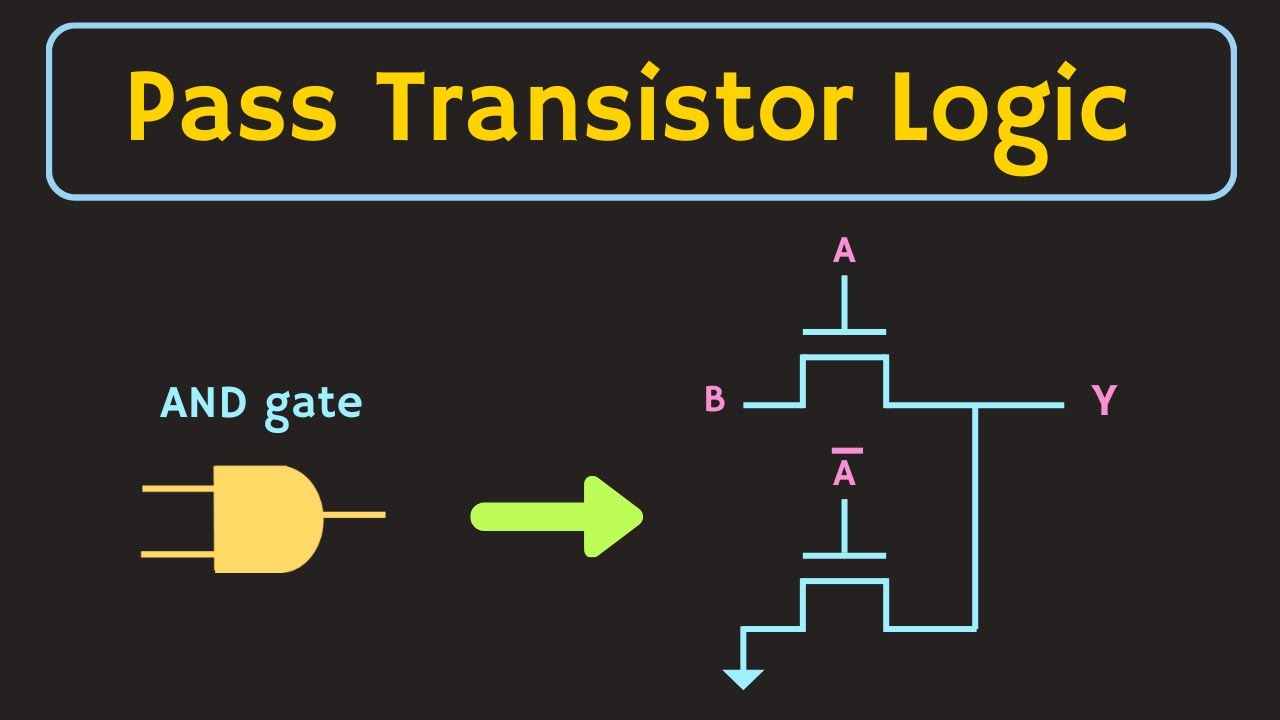

Vlsi Design Pass Transistor Logic Youtube Reading assignment – rabaey, et al, 4.14.3.1. in1 in2 inn. pdn. f(in1,in2,inn) pun and pdn are dual logic networks. never a direct path between. v and gnd in steady state. dd. delay a function of load capacitance and transistor on resistance comparable rise and fall times (under the appropriate relative transistor sizing conditions). Low output impedance, high input impedance. no static power consumption. f(in1,in2, inn) in1 in2 inn. pdn. pun and pdn are dual logic networks. never a direct path between vdd and gnd in steady state. . delay a function of load capacitance and transistor on resistance. comparable rise and fall times (under the appropriate relative transistor. Remember nmos transistors pass a strong 0 but a weak 1 ab xy x = y if a and b xy a b x = y if a or b comp103 l7.4 pmos transistors in series parallel primary inputs drive both gate and source drain terminals pmos switch closes when the gate input is low remember pmos transistors pass a strong 1 but a weak 0 ab xy x = y if a and b = a b xy a. Very popular in vlsi design practices. a methodology for synthesis of pass transistor functions was established presenting a modified karnaugh map which employs the pass variables, not only logic zeroes and ones. a formal design procedure for pass transistor switching circuits was developed later in [whitaker, jo ssc]. this work was further.

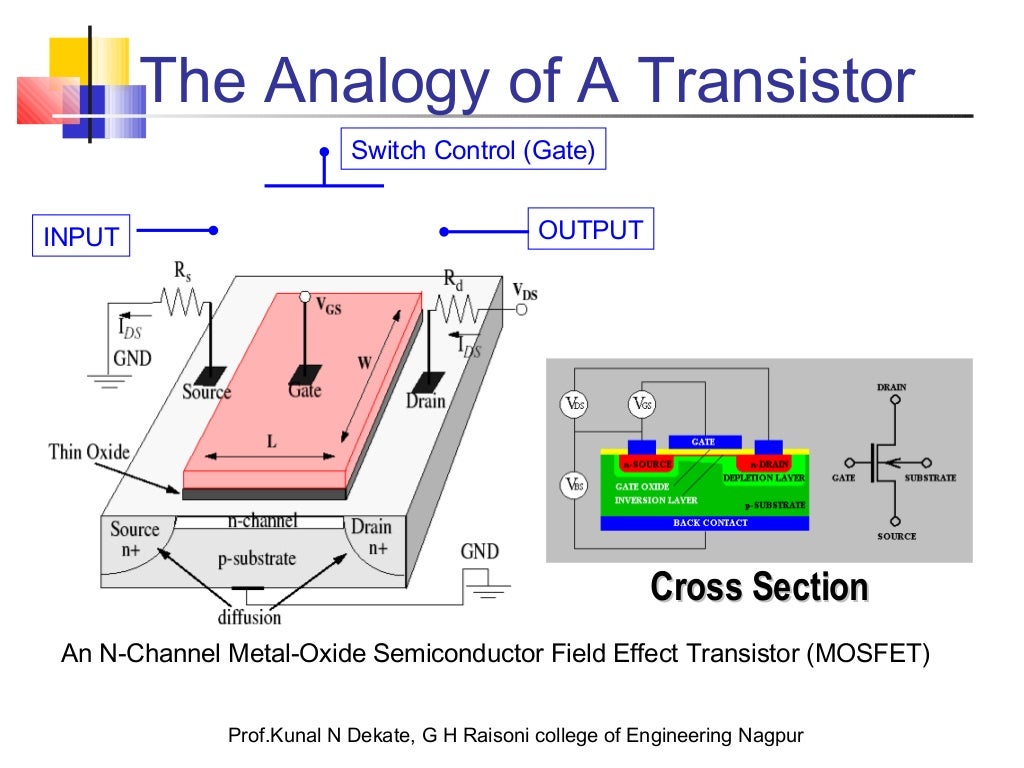

Vlsi Design Chapter 5 Cmos Circuit And Logic Remember nmos transistors pass a strong 0 but a weak 1 ab xy x = y if a and b xy a b x = y if a or b comp103 l7.4 pmos transistors in series parallel primary inputs drive both gate and source drain terminals pmos switch closes when the gate input is low remember pmos transistors pass a strong 1 but a weak 0 ab xy x = y if a and b = a b xy a. Very popular in vlsi design practices. a methodology for synthesis of pass transistor functions was established presenting a modified karnaugh map which employs the pass variables, not only logic zeroes and ones. a formal design procedure for pass transistor switching circuits was developed later in [whitaker, jo ssc]. this work was further. Implementing logic in cmos jacob abraham, september 3, 2020 1 37. static cmos circuits. n and p channelnetworks n and p channel networks implement logic functions. each network connected betweenoutput and vddor vss. function de nes path between the terminals. ece department, university of texas at austin lecture 3. Dd and gnd (no static power consumption) delay a function of load capacitance and transistor resistance comparable rise and fall times (under the appropriate transistor sizing conditions) dynamic cmos relies on temporary storage of signal values on the capacitance of high impedance circuit nodes simpler, faster gates.

Pass Transistor Logic Explained How To Implement Logic Gates Using Implementing logic in cmos jacob abraham, september 3, 2020 1 37. static cmos circuits. n and p channelnetworks n and p channel networks implement logic functions. each network connected betweenoutput and vddor vss. function de nes path between the terminals. ece department, university of texas at austin lecture 3. Dd and gnd (no static power consumption) delay a function of load capacitance and transistor resistance comparable rise and fall times (under the appropriate transistor sizing conditions) dynamic cmos relies on temporary storage of signal values on the capacitance of high impedance circuit nodes simpler, faster gates.

Fundamentals Of Cmos Vlsi Design And Mos Transistors

Comments are closed.