Chapter 7 Complementary Mos Cmos Logic Design Microelectro

Chapter 7 Complementary Mos Cmos Logic Design Microelectro 35 complex cmos logic gate design example by placing nodes in the interior of each arc, plus two more outside the graph for vdd (3) and the complementary output (2’), the pmos branch can be realized as shown on the left figure connect all of the nodes in the manner shown in the right figure, and the nmos arc that pmos arc intersects have the same inputs microelectronic circuit design mcgraw hill. Cmos inverter technology. • complementary mos, or cmos, needs both pmos and nmos. devices for the logic gates to be realized. • the concept of cmos was introduced in 1963 by wanlass and sah. • cmos are more complicated in design and production, thus are more. expensive to fabricate.

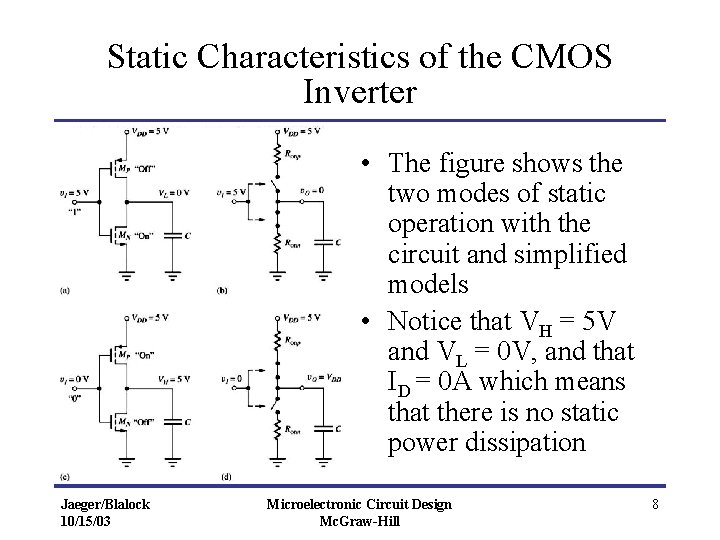

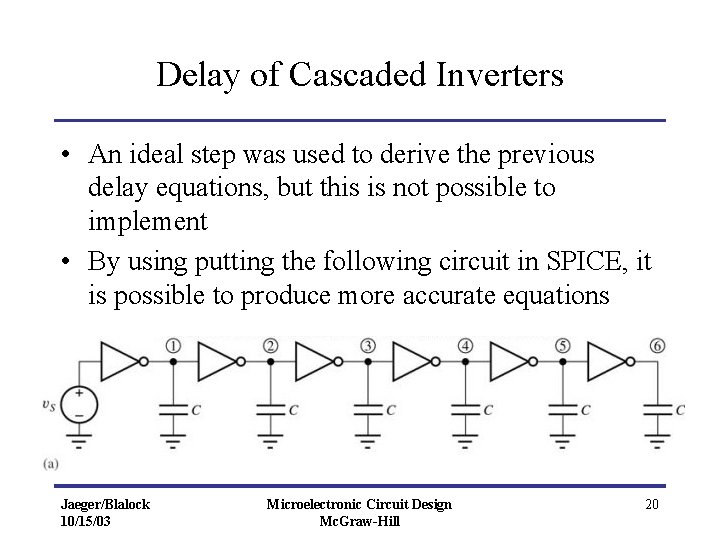

Chapter 7 Complementary Mos Cmos Logic Design Microelectro Chapter 7complementary mos (cmos) logic design microelectronic circuit design richard c. jaegertravis n. blalock microelectronic circuit design, 4e mcgraw hill. chapter goals • introduce cmos logic concepts • explore the voltage transfer characteristics of cmos inverters • learn to design basic and complex cmos logic gates • discuss the static and dynamic power in cmos logic. Cmos inverter: propagation delay. inverter propagation delay: time delay between input and output signals; key figure of merit of logic speed. typical propagation delays: < 1 ns. complex logic system has 20 50 propagation delays per clock cycle. estimation of tp: use square wave at input. vin. vdd. Multi input cmos nand gates microelectronic circuit design mcgraw hill. complex cmos logic gate design example • design a cmos logic gate for (w l)p,ref=5 1 and for (w l)n,ref=2 1 that exhibits the function: y = a bc bd • by inspection (knowing y), the nmos branch of the gate can drawn as the following with the corresponding graph, while. Mos inverter circuits outline • nmos inverter with resistor pull up –the inverter • nmos inverter with current source pull up • complementary mos (cmos) inverter • static analysis of cmos inverter reading assignment: howe and sodini; chapter 5, section 5.4 6.012 spring 2009 lecture 12 1.

Comments are closed.